版权所有: SHEN ZHEN KOYU ELECTRONICS CO.,LTD深圳市光与电子有限公司 Copyright © 2022 All Rights reserved. 粤ICP备19162453号

技术方案

AMAZINGIC晶焱科技:Ethernet网口的ESD/EOS防护方案

发布时间:2024-05-30 09:51:55

AMAZINGIC晶焱科技:Ethernet网口的ESD/EOS防护方案

网口在NB、MB、IP-CAM等产品上属于相当常见的端口,因网络有可能布线至户外,受到EOS突波干扰而造成网络功能异常的机率较高,故有必要在网口设计有效率的ESD/EOS防护对策。

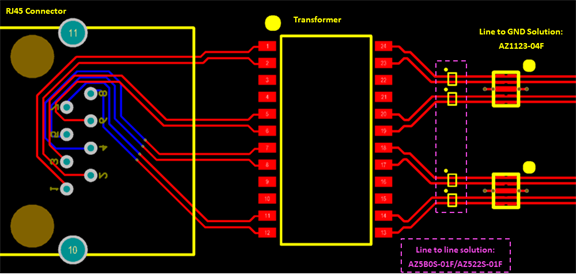

如图一所示,网口的架构由外部往内可大致切分成3大部分:(1) RJ45 connector, (2) Transformer, (3) LAN PHY。(1)至(2)之间称之为一次侧(Primary side),当Surge测试规格较高时,在一次侧transformer中心抽头处可考虑采用高Surge耐受度的元件保护Bob Smith电路;(2)至(3)之间则为二次侧(Secondary side),最新的电路设计趋势是将保护器件设计在此区域,用以将transformer隔离过后的突波能量进一步抑制,大幅降低后端LAN PHY受外界异常干扰的威胁。

图一、网口架构示意图

网口的Surge测试会分为Differential mode和Common mode两个测试项来进行,故在防护对策上的建议用料亦有所不同。Differential mode主要是针对差动信号线之间做Surge测试,此时会建议采用双向保护元件,在differential mode Surge测试时Surge元件导通示意如图二所示。

图二、Differential mode Surge test 防护元件导通示意图

Common mode Surge是将所有网络信号线同时对地做Surge测试,此时虽然一次侧可宣泄大部分能量,但亦会有少部分能量耦合至二次侧,此时二次侧的ESD/EOS保护元件将启动把Common mode Surge测试时的能量宣泄至地,示意如图三所示。

图三、Common mode Surge test 防护元件导通示意图

| Interface | Protection | Parts | Package | VRWM (V) | VBR (V) | Vclamp(ESD) | CIn(Typ.) | Ipp(8/20µs) |

|---|---|---|---|---|---|---|---|---|

| 10/100/1000Mbps Ethernet |

Line to GND | AZ1213-04F | 4 I/O Pins DFN2510P10E 2.5x1.0x0.5 mm |

3.3 | 5 | 6.5 | 2.1pF | 20A |

| Line to Line | AZ3125-08F | 4 I/O Pins DFN3020P10E 3x2x0.55 mm |

2.5 | 3 | 8 | 1.7pF | 45A | |

| LED control signal | AZ5883-01F | 1 I/O Pins DFN1006P2E 1.0x0.6x0.5 mm |

3.3 | 4.5 | 5 | 70pF | 52A | |

| 2.5/5/10Gbps Ethernet |

Line to GND | AZ1123-04F | 4 I/O Pins DFN2510P10E 2.5x1.0x0.5 mm |

3.3 | 5 | 10 | 0.2pF | 6.5A |

| Line to Line | AZ5B0S-01F | 1 I/O Pins DFN0603P2Y 0.6x0.3x0.3 mm |

2 | 5.5 | 5.5 | 0.18pF | 7A | |

| Line to Line | AZ522S-01F | 1 I/O Pins DFN1006P2E 1.0x0.6x0.5 mm |

2 | 5.5 | 6.5 | 0.2pF | 6.5A | |

| LED control signal | AZ5883-01F | 1 I/O Pins DFN1006P2E 1.0x0.6x0.5 mm |

3.3 | 4.5 | 5 | 70pF | 42A |

表一、Ethernet ESD/EOS保护方案一览表

晶焱科技对于网口ESD/EOS完整对策如表一所示,以10Gbps网口为例,Differential mode防护的建议料件有两种封装选择,分别为DFN0603P2Y(0201)封装的AZ5B0S-01F或DFN1006P2E(0402)封装的AZ522S-01F,这两颗元件的寄生电容皆在0.2pF左右,单体皆可承受IEC61000-4-5 Surge (8/20μs) 约6.5A。Common mode的防护对策则推荐4通道的防护对策AZ1123-04F,寄生电容亦在0.2pF左右,单体亦可承受IEC61000-4-5 Surge (8/20μs)约6.5A。AZ1123-04F的封装为DFN2510P10E,PCB Layout走线可采顺线(feed-through)方式,设计上非常便利,可参考图四的示意图。上述10Gbps网口EOS/ESD防护对策中,推荐的防护元件本身寄生电容小,对信号品质影响较小,且单体耐受佳,非常适合放在网口高速信号上使用。

图四、10Gbps网口ESD/EOS元件PCB Layout示意图

此外,根据长年来进行网口进行ESD/EOS测试的经验,较常遇到EOS或ESD (Air Discharge)能量耦合至RJ45 LED控制信号,导致LAN PHY损坏的问题,如图五所示。故建议在设计线路时,在LED的控制信号线亦加上防护对策,以避免此问题的发生。

图五、网口ESD测试示意图

网络已成大众生活中必备的工具,故建议在设计系统的初期就先将相应的防护对策设计至电路中,以避免未来安规测试无法通过的难题,同时可降低市场上因EOS/ESD而导致网口不良的问题发生。若因成本因素决定不在较低阶机种进行防护,亦建议在相关位置设计预留保护元件的封装位置,避免日后遭遇市场返修问题,甚或品牌客户要求提高规格时需要再花费时间及物力进行改版的难题。