版权所有: SHEN ZHEN KOYU ELECTRONICS CO.,LTD深圳市光与电子有限公司 Copyright © 2022 All Rights reserved. 粤ICP备19162453号

技术方案

AMAZINGIC晶焱科技:TVS Array layout时应注意的事项

发布时间:2024-05-30 09:52:40

AMAZINGIC晶焱科技:TVS Array layout时应注意的事项

近年随着电子产品小型化的趋势,R & D研发人员在设计产品时往往会面临到因PCB空间较小而造成PCB GND的宣泄路径不佳,容易导致无法通过ESD/EOS测试的问题,为了顺利通过IEC-61000-4-2及IEC-61000-4-5防护测试规范,R & D研发人员在系统电路上配置防护元件就变得格外重要,若防护元件配置的位置及走线方式不 佳,则会导致无法发挥防护元件应有的效果,最终将导致主晶片受到ESD/EOS的影响,造成系统损坏或I/O端口功能出现异常。 本文主要介绍在进行防护电路设计时,需要特别留意的防护元件位置及PCB Layout走线方式等事项,适用于目前市面上各式不同封装的防护元件。

1. ESD/EOS保护元件配置位置的注意事项

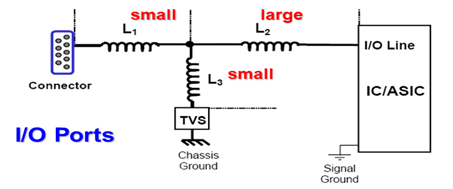

图一 :拆解保护元件在PCB Layout时配置位置的各项参数

● 如图一L1 - 指PCB Layout 时Connector与TVS的距离,建议这段距离应尽可能缩短,同时需确认Connector后第一个接触的零件为TVS防护元件。 主要目的是减少ESD/EOS瞬态能量在未通过TVS防护元件前,能量就耦合到附近或下层的敏感高速讯号trace或是电源路径的可能性。 其次,瞬态能量进入connector后到TVS防护元件宣泄至地的距离越短,回路所造成的电磁波干扰也越小。 除此之外,若瞬态能量在接触TVS防护元件前先通过如 Common Mode Choke, 电容或电阻等元件,则会溢散出电磁波干扰系统运作,造成系统功能异常或当机。

● L2 - 指在TVS保护元件和Chipset的I/O之间的距离。 在connector到Chipset IC总长度不变的前提下,若前述L1越短则L2越长,如此可助于放电路径上电感值增加,进而减少流往L2的分流电流并降低流至Chipset IC端的瞬态电压振幅。 甚至亦有产品在设计时,直接利用绕线的方式拉长L2的长度做为辅助达成ESD/EOS设计目标的方法。

● 如图一所示L3- 指为了连接TVS保护元件,在原有I/O trace上外加的T字形分支Layout走线路径。 ESD/EOS瞬态突波电流在流经此L3所造成的寄生电感时,将直接造成整体钳制电压的提升,对保护电路的设计的影响非常巨大。 因此,进行设计时应尽可能使L3能够越小越好,让TVS防护元件不会因其L3所带来的效应,而造成防护效果不佳。

● 需额外注意的是,若TVS接地时亦需要直接接到大面积GND层,若采用GND trace的设计则亦会在此处造成额外的电感,同样将直接拉高整体钳制电压表现,严重影响 保护电路的设计功效。

2. TVS防护元件在PCB Layout的注意事项(此以USB2.0端为范例)

图二、6-pin TVS防护元件在dual USB2.0端的Layout范例

● TVS防护元件的VDD脚位建议直接连接至USB Port VBUS电源trace,尽量避免上述的T字形分支trace或穿层时VIA造成的电感影响。

● TVS防護元件的GND腳位應直接與PCB Layout中大面積的GND層直接連接,避免使用PCB Trace連接防護元件的GND腳。

● 如图二所示,在进行多通道TVS保护元件的PCB Layout时,VDD或GND脚可能需要使用VIA连接,建议设计时采用两个或两个以上VIA过孔连接进行PCB 穿层,目的为 降低接地阻抗值及降低电感效应。

● 如图二所示,6-pin TVS的位置已尽量接近Connector,布线亦应尽量缩短。 避免前述耦合至邻近或下层讯号或电源路径的可能性,亦尽可能降低宣泄ESD/EOS能量时产生的电磁波干扰。

● 进行讯号线防护设计时,应尽可能将TVS保护元件的PAD直接设计于讯号线trace上,避免T字形分支路径额外造成的电感影响保护元件的功效,亦可参考以下之实际layout案例比较。

案例一 : 错误的PCB Layout方式

图三、错误的保护元件Layout方式

如图三中讯号线的PCB Layout是透过T字分支的路径(如图三蓝色框处所示)连接到保护元件,将会导致保护电路钳制电压上升,增加ESD/EOS能量往内部电路分流的风险,最终可能导致保护元件无法发挥其应有的效果。

案例二 : 正确的PCB Layout方式

图四、正确的防护元件Layout方式

如图四中讯号线的PCB Layout是将防护元件PAD直接设计在讯号的走线上,符合图二中讯号线的layout guideline,并未造成额外的T字分支路径(如图四蓝色框处所 示),可确保ESD/EOS能量由Connector进入时,防护元件可发挥最佳的防护效果。

总结 :

随着电子产品小型化的趋势,需留意防护元件在PCB上的摆放位置及Layout方式,避免错误的布线导致ESD/EOS防护效果不好。 故在设计保护电路时,在选择正确及有效的TVS防护元件后,妥善完成PCB Layout布线也是影响最终防护结果的重要环节。